Table of Contents

Advertisement

Quick Links

Advertisement

Table of Contents

Summary of Contents for Asus AAEON GENE-APL6

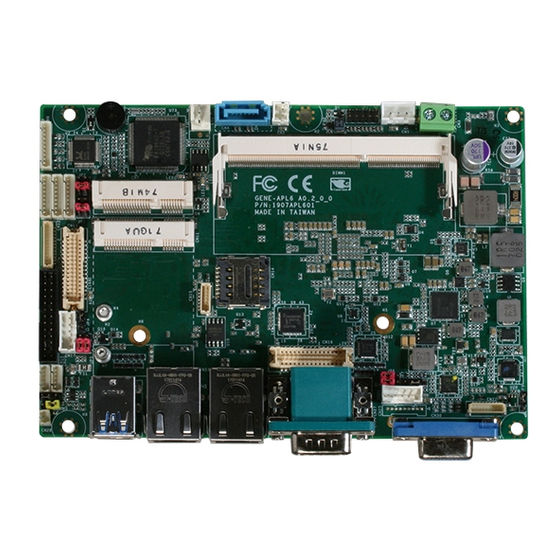

- Page 1 GENE-APL6 3.5” Subcompact Board User’s Manual 3 Last Updated: June 13, 2019...

- Page 2 Copyright Notice This document is copyrighted, 2019. All rights are reserved. The original manufacturer reserves the right to make improvements to the products described in this manual at any time without notice. No part of this manual may be reproduced, copied, translated, or transmitted in any form or by any means without the prior written permission of the original manufacturer.

- Page 3 Acknowledgement All other products’ name or trademarks are properties of their respective owners. Microsoft Windows is a registered trademark of Microsoft Corp. Intel, Pentium, Celeron, and Xeon are registered trademarks of Intel Corporation Core, Atom are trademarks of Intel Corporation ...

- Page 4 Packing List Before setting up your product, please make sure the following items have been shipped: Item Quantity GENE-APL6 with heat spreader If any of these items are missing or damaged, please contact your distributor or sales representative immediately. Preface...

- Page 5 About this Document This User’s Manual contains all the essential information, such as detailed descriptions and explanations on the product’s hardware and software features (if any), its specifications, dimensions, jumper/connector settings/definitions, and driver installation instructions (if any), to facilitate users in setting up their product. Users may refer to the AAEON.com for the latest version of this document.

- Page 6 Safety Precautions Please read the following safety instructions carefully. It is advised that you keep this manual for future references All cautions and warnings on the device should be noted. Make sure the power source matches the power rating of the device. Position the power cord so that people cannot step on it.

- Page 7 If any of the following situations arises, please the contact our service personnel: Damaged power cord or plug Liquid intrusion to the device iii. Exposure to moisture Device is not working as expected or in a manner as described in this manual The device is dropped or damaged Any obvious signs of damage displayed on the device...

- Page 8 FCC Statement This device complies with Part 15 FCC Rules. Operation is subject to the following two conditions: (1) this device may not cause harmful interference, and (2) this device must accept any interference received including interference that may cause undesired operation.

- Page 9 China RoHS Requirements (CN) 产品中有毒有害物质或元素名称及含量 AAEON Main Board/ Daughter Board/ Backplane 有毒有害物质或元素 部件名称 铅 汞 镉 六价铬 多溴联苯 多溴二苯醚 (Pb) (Hg) (Cd) (Cr(VI)) (PBB) (PBDE) 印刷电路板 ○ ○ ○ ○ ○ ○ 及其电子组件 外部信号 ○ ○ ○ ○ ○ ○ 连接器及线材...

- Page 10 China RoHS Requirement (EN) Poisonous or Hazardous Substances or Elements in Products AAEON Main Board/ Daughter Board/ Backplane Poisonous or Hazardous Substances or Elements Hexavalent Polybrominated Polybrominated Component Lead Mercury Cadmium Chromium Biphenyls Diphenyl Ethers (Pb) (Hg) (Cd) (Cr(VI)) (PBB) (PBDE) PCB &...

-

Page 11: Table Of Contents

Table of Contents Chapter 1 - Product Specifications..................1 Specifications ......................2 Chapter 2 – Hardware Information ..................5 Dimensions ....................... 6 2.1.1 Dimensions (Optional HDMI SKU) ............. 9 Jumpers and Connectors ..................12 2.2.1 Jumpers and Connectors (Optional HDMI SKU)......13 Assembly Options ....................14 Block Diagram ......................14 List of Jumpers ...................... - Page 12 2.5.6 Audio I/O Port (CN6) ................26 2.5.7 Mini-Card Slot (Full-Size) (CN7) ............27 2.5.8 COM Port 2 (CN8) ................29 2.5.9 COM Port 3 (CN9) ................31 2.5.10 COM Port 4 (CN10) ................33 2.5.11 mSATA Slot (Half-Size) (CN11) ............35 2.5.12 LPC Port (CN12) ...................

- Page 13 AMI BIOS Setup ..................... 63 Setup submenu: Main ..................64 Setup submenu: Advanced ................. 65 3.4.1 Advanced: Trusted Computing ............66 3.4.2 Advanced: CPU Configuration ............68 3.4.3 Advanced: SATA Configuration ............70 3.4.4 Advanced: SCC Configuration ............72 3.4.5 Advanced: PCI Express Configuration ..........

- Page 14 Watchdog Timer Registers .................. 97 Watchdog Sample Program ................98 Appendix B - I/O Information ....................101 I/O Address Map ....................102 Memory Address Map ..................104 IRQ Mapping Chart ..................... 105 Appendix C – Mating Connectors ..................109 List of Mating Connectors and Cables ............. 110 Appendix D –...

-

Page 15: Chapter 1 - Product Specifications

Chapter 1 Chapter 1 - Product Specifications... -

Page 16: Specifications

Specifications System 3.5'' SubCompact Board Form Factor Intel® Pentium® N4200/ Celeron® N3350 Processor SoC up to 2.5GHz CPU Frequency Intel® Pentium® N4200/ Celeron® N3350 Chipset Processor SoC DDR3L 1866MHz, SODIMM x 1 Memory Type Up to 8GB Max. Memory Capacity UEFI BIOS Wake on LAN... - Page 17 System CE/FCC Certification Intel® i210/I211, 10/100/1000Base-TX, RJ-45 x 2 Ethernet High Definition Audio Interface Audio USB 3.0 x 2 USB Port USB 2.0 x 2 RS-232 x 2 , RS-232/422/485 x 2 Serial Port SPP/EPP/ECP x 1 (Option, Shared with DIO) Parallel Port SATA 3.0 x 1 HDD Interface...

- Page 18 Display Intel® Pentium® N4200/ Celeron® N3350 VGA/LCD Controller Processor SoC LVDS, LVDS2, VGA (HDMI is option, co-layout Video Output with LVDS2) Backlight Inverter Supply Chapter 1 – Product Specifications...

-

Page 19: Chapter 2 - Hardware Information

Chapter 2 Chapter 2 – Hardware Information... -

Page 20: Dimensions

Dimensions Component Side Chapter 2 – Hardware Information... - Page 21 Solder Side Chapter 2 – Hardware Information...

- Page 22 With Heat Spreader Chapter 2 – Hardware Information...

-

Page 23: Dimensions (Optional Hdmi Sku)

2.1.1 Dimensions (Optional HDMI SKU) Component Side Chapter 2 – Hardware Information... - Page 24 Solder Side Chapter 2 – Hardware Information...

- Page 25 With Heat Spreader Chapter 2 – Hardware Information...

-

Page 26: Jumpers And Connectors

Jumpers and Connectors Component Side Chapter 2 – Hardware Information... -

Page 27: Jumpers And Connectors (Optional Hdmi Sku)

2.2.1 Jumpers and Connectors (Optional HDMI SKU) Component Side Chapter 2 – Hardware Information... -

Page 28: Assembly Options

Assembly Options Optional accessory for GENE-APL6-HSK01 Block Diagram Chapter 2 – Hardware Information... - Page 29 Chapter 2 – Hardware Information...

-

Page 30: List Of Jumpers

List of Jumpers Please refer to the table below for all of the board’s jumpers that you can configure for your application Label Function Front Panel Connector COM2 Pin8 Function Selection COM3 Pin8 Function Selection LVDS Port2 Backlight Lightness Control Mode Selection LVDS Port2 Backlight Inverter VCC Selection and Operating VDD Selection LVDS Port1 Backlight Inverter VCC Selection... -

Page 31: Front Panel Connector (Jp1)

2.4.1 Front Panel Connector (JP1) Pin Name Pin Name PWR_BTN- PWR_BTN+ HDD_LED- HDD_LED+ SPEAKER- SPEAKER+ PWR_LED- PWR_LED+ H/W RESET- H/W RESET+ 2.4.2 COM2 Pin8 Function Selection (JP2) Ring(Default) +12V Chapter 2 – Hardware Information... -

Page 32: Com3 Pin8 Function Selection (Jp3)

2.4.3 COM3 Pin8 Function Selection (JP3) Ring(Default) +12V 2.4.4 LVDS Port2 Backlight Lightness Control Mode Selection (JP4) VR Mode (Default) PWM Mode 2.4.5 VDS Port2 Backlight Inverter VCC Selection (JP5) +12V +5V (Default) Chapter 2 – Hardware Information... -

Page 33: Vds Port1 Backlight Inverter Vcc Selection (Jp6)

+3.3V (Default) 2.4.6 VDS Port1 Backlight Inverter VCC Selection (JP6) +12V +5V (Default) +3.3V (Default) Chapter 2 – Hardware Information... -

Page 34: Lvds Port1 Backlight Lightness Control Mode Selection (Jp7)

2.4.7 LVDS Port1 Backlight Lightness Control Mode Selection (JP7) VR Mode (Default) PWM Mode 2.4.8 Auto Power Button Enable/Disable Selection (JP8) 1 2 3 Disable/ATX Enable/AT (Default) ※ When disabled, the power button of JP5 (1-2) will be used to power on the system 2.4.9 Touch Screen 4,5,8 Wire Selection (JP9) 4/8 Wires Mode (Default) 5 Wires Mode... -

Page 35: Clear Cmos Jumper (Jp10)

2.4.10 Clear CMOS Jumper (JP10) 1 2 3 Normal (Default) Clear CMOS Chapter 2 – Hardware Information... -

Page 36: List Of Connectors

List of Connectors Please refer to the table below for all of the board’s connectors that you can configure for your application Label Function External +5VSB Input +5V Output for SATA HDD External Power Input SATA Port CPU FAN (Optional) Audio I/O Port Mini-Card Slot (Full-Size) COM Port 2... - Page 37 Label Function CN24 LAN (RJ-45) Port2 CN25 COM Port 1 (Wafer, Optional) CN26 USB3.0 Port 0 / Port 1 CN27 COM Port 1(D-SUB 9) CN28 Battery CONN CN29 HDMI CONN CN30 VGA Port DIMM1 DDR3L SO-DIMM Slot Chapter 2 – Hardware Information...

-

Page 38: External +5Vsb Input (Cn1)

2.5.1 External +5VSB Input (CN1) PS_ON# +5VSB Pin Name Signal Type Signal level PS_ON# +5VSB ※ Since every power supply discharge design is different, we recommend restarting 3 seconds after powering off to make sure ATX power is fully discharged. Or, make sure 5V standby power has been discharged under 2V. 2.5.2 +5V Output for SATA HDD (CN2) Pin Name Signal Type... -

Page 39: External Power Input (Cn3)

2.5.3 External Power Input (CN3) Pin Name Signal Type Signal Level +VIN 9V~36V or 12V ※There are two types of power input, 9V~36V or 12V only, by BOM Change 2.5.4 SATA Port (CN4) Pin 1 Pin 7 Pin Name Signal Type Signal Level SATA_TX+ DIFF... -

Page 40: Audio I/O Port (Cn6)

Pin Name Signal Type Signal Level FAN_POWER +12V FAN_TAC 2.5.6 Audio I/O Port (CN6) MIC_L MIC_R GND_AUDIO LINE_L_IN LINE_R_IN GND_AUDIO LEFT_OUT GND_AUDIO RIGHT_OUT +5V_AUDIO Pin Name Signal Type Signal Level MIC_L MIC_R GND_AUDIO LINE_L_IN LINE_R_IN GND_AUDIO Chapter 2 – Hardware Information... -

Page 41: Mini-Card Slot (Full-Size) (Cn7)

LEFT_OUT GND_AUDIO RIGHT_OUT +5V_AUDIO 2.5.7 Mini-Card Slot (Full-Size) (CN7) Pin Name Signal Type Signal Level PCIE_WAKE# +3.3V +3.3VSB +1.5V +1.5V PCIE_CLK_REQ# UIM_PWR UIM_DATA PCIE_REF_CLK- DIFF UIM_CLK PCIE_REF_CLK+ DIFF UIM_RST Chapter 2 – Hardware Information... - Page 42 Pin Name Signal Type Signal Level UIM_VPP W_DISABLE# +3.3V PCIE_RST# +3.3V PCIE_RX- DIFF +3.3VSB +3.3V PCIE_RX+ DIFF +1.5V +1.5V SMB_CLK +3.3V PCIE_TX- DIFF SMB_DATA +3.3V PCIE_TX+ DIFF USB_D- DIFF Chapter 2 – Hardware Information...

-

Page 43: Com Port 2 (Cn8)

Pin Name Signal Type Signal Level USB_D+ DIFF +3.3VSB +3.3V +3.3VSB +3.3V +1.5V +1.5V +3.3VSB +3.3V 2.5.8 COM Port 2 (CN8) Chapter 2 – Hardware Information... - Page 44 RS232 Pin Name Signal Type Signal Level DCD2 DSR2 RTS2 ±5V ±5V CTS2 DTR2 ±5V RI2/+5V/+12V +5V/+12V Chapter 2 – Hardware Information...

-

Page 45: Com Port 3 (Cn9)

RS485 Pin Name Signal Type Signal Level RS485_ D2- ±5V RS485_D2+ ±5V NC/+5V/+12V +5V/+12V RS422 Pin Name Signal Type Signal Level RS422_TX2- ±5V RS422_TX2+ ±5V RS422_RX2+ RS422_RX2- NC/+5V/+12V +5V/+12V ※ COM2 RS-232/422/485 can be set by BIOS setting. Default is RS-232. ※... - Page 46 RS232 Pin Name Signal Type Signal Level DCD3 DSR3 RTS3 ±5V ±5V CTS3 DTR3 ±5V RI2/+5V/+12V +5V/+12V Chapter 2 – Hardware Information...

-

Page 47: Com Port 4 (Cn10)

RS485 Pin Name Signal Type Signal Level RS485_ D3- ±5V RS485_D3+ ±5V NC/+5V/+12V +5V/+12V RS422 Pin Name Signal Type Signal Level RS422_TX3- ±5V RS422_TX3+ ±5V RS422_RX3+ RS422_RX3- NC/+5V/+12V +5V/+12V ※ COM3 RS-232/422/485 can be set by BIOS setting. Default is RS-232 ※... - Page 48 Pin Name Signal Type Signal Level DCD4 DSR4 RTS4 ±9V ±9V CTS4 DTR4 ±9V Chapter 2 – Hardware Information...

-

Page 49: Msata Slot (Half-Size) (Cn11)

2.5.11 mSATA Slot (Half-Size) (CN11) Pin Name Signal Type Signal Level +3.3V +3.3V SRXP_PRXN DIFF Chapter 2 – Hardware Information... - Page 50 +3.3V +3.3V SRXN_PRXP DIFF STXN_PTXN DIFF STXP_PTXP DIFF +3.3V +3.3V +3.3V +3.3V Chapter 2 – Hardware Information...

-

Page 51: Lpc Port (Cn12)

+3.3V +3.3V 2.5.12 LPC Port (CN12) Pin Name Signal Type Signal Level LAD0 +3.3V LAD1 +3.3V LAD2 +3.3V LAD3 +3.3V +3.3V +3.3V LFRAME# LRESET# +3.3V LCLK Chapter 2 – Hardware Information... -

Page 52: Lvds Port2 (Cn13)

SMB_DATA/I2C_SDA SMB_CLK/I2C_CLK +3.3V SMB_ALERT/SERIRQ 2.5.13 LVDS Port2 (CN13) ※ LVDS LCD_PWR2 can be set to +3.3V or +5V by JP5 Pin Name Signal Type Signal Level BKL_ENABLE2 BKL_CONTROL2 LCD_PWR2 +3.3V/+5V LVDS2_A_CLK- DIFF Chapter 2 – Hardware Information... - Page 53 LVDS2_A_CLK+ DIFF LCD_PWR2 +3.3V/+5V LVDS2_DA0- DIFF LVDS2_DA0+ DIFF LVDS2_DA1- DIFF LVDS2_DA1+ DIFF LVDS2_DA2- DIFF LVDS2_DA2+ DIFF LVDS2_DA3- DIFF LVDS2_DA3+ DIFF DDC2_DATA +3.3V DDC2_CLK +3.3V LVDS2_DB0- DIFF LVDS2_DB0+ DIFF LVDS2_DB1- DIFF LVDS2_DB1+ DIFF LVDS2_DB2- DIFF LVDS2_DB2+ DIFF LVDS2_DB3- DIFF LVDS2_DB3+ DIFF LCD_PWR2 +3.3V/+5V LVDS2_B_CLK-...

-

Page 54: Micro Sim Card Socket (Cn14)

2.5.14 Micro SIM Card Socket (CN14) Pin Name Signal Type Signal Level UIM_PWR UIM_RST UIM_CLK UIM_VPP UIM_DATA Chapter 2 – Hardware Information... -

Page 55: Bios Debug Port (Cn15)

2.5.15 BIOS Debug Port (CN15) Pin Name Signal Type Signal Level SPI_MISO SPI_CLK +3.3VSB +3.3V SPI_MOSI SPI_CS Chapter 2 – Hardware Information... -

Page 56: Lpt Port Or Digital I/O Port (Cn16)

2.5.16 LPT Port or Digital I/O Port (CN16) AFD# STROBE# ERROR# PRINT# SLIN# ACK# BUSY SLCT ※ LPT or Digital I/O function can be selected by BIOS setting. Default is LPT port LPT Port Pin Name Signal Type Signal Level STROBE# AFD# ERROR#... - Page 57 ACK# BUSY SLCT Chapter 2 – Hardware Information...

- Page 58 Digital I/O Port Pin Name Signal Type Signal Level DIO0 DIO1 DIO2 DIO3 DIO4 DIO5 DIO6 Chapter 2 – Hardware Information...

-

Page 59: Lvds Port2 Inverter / Backlight Connector (Cn17)

DIO7 2.5.17 LVDS Port2 Inverter / Backlight Connector (CN17) Pin Name Signal Type Signal Level BKL_PWR +5V / +12V BKL_CONTROL BKL_ENABLE ※ LVDS2 BKL_PWR can be set to +5V or +12V by JP5 ※ LVDS2 BKL_CONTROL can be set by JP4 2.5.18 LVDS Port1 (CN18) Chapter 2 –... - Page 60 ※ LVDS1 LCD_PWR can be set to +3.3V or +5V by JP1. Pin Name Signal Type Signal Level BKL_ENABLE BKL_CONTROL LCD_PWR +3.3V/+5V LVDS_A_CLK- DIFF LVDS_A_CLK+ DIFF LCD_PWR +3.3V/+5V LVDS_DA0- DIFF LVDS_DA0+ DIFF LVDS_DA1- DIFF LVDS_DA1+ DIFF Chapter 2 – Hardware Information...

-

Page 61: Usb 2.0 Port 4 (Cn19)

Pin Name Signal Type Signal Level LVDS_DA2- DIFF LVDS_DA2+ DIFF LVDS_DA3- DIFF LVDS_DA3+ DIFF DDC_DATA +3.3V DDC_CLK +3.3V LVDS_DB0- DIFF LVDS_DB0+ DIFF LVDS_DB1- DIFF LVDS_DB1+ DIFF LVDS_DB2- DIFF LVDS_DB2+ DIFF LVDS_DB3- DIFF LVDS_DB3+ DIFF LCD_PWR +3.3V/+5V LVDS_B_CLK- DIFF LVDS_B_CLK+ DIFF 2.5.19 USB 2.0 Port 4 (CN19) Chapter 2 –... - Page 62 Pin Name Signal Type Signal Level +5VSB USB_D- DIFF USB_D+ DIFF Chapter 2 – Hardware Information...

-

Page 63: Usb 2.0 Port 5 (Cn20)

2.5.20 USB 2.0 Port 5 (CN20) Pin Name Signal Type Signal Level +5VSB USB_D- DIFF USB_D+ DIFF 2.5.21 LVDS Port1 Inverter / Backlight Connector (CN21) Pin Name Signal Type Signal Level BKL_PWR +5V / +12V BKL_CONTROL Chapter 2 – Hardware Information... -

Page 64: Touch Screen Connector (Optional) (Cn22)

Pin Name Signal Type Signal Level BKL_ENABLE ※ LVDS1 BKL_PWR can be set to +5V or +12V by JP6 ※ LVDS1 BKL_CONTROL can be set by JP7 2.5.22 Touch Screen Connector (Optional) (CN22) 8-Wire Pin Name Signal Type Signal Level TOP EXCITE BOTTOM EXCITE LEFT EXCITE... - Page 65 LEFT SENSE RIGHT SENSE 4-Wire Pin Name Signal Type Signal Level BOTTOM LEFT RIGHT Chapter 2 – Hardware Information...

- Page 66 5-Wire Pin Name Signal Type Signal Level UL(Y) UR(H) LL(L) LR(X) SENSE(S) ※ Touch mode can be set by BIOS setting Chapter 2 – Hardware Information...

-

Page 67: Lan (Rj-45) Port1 (Cn23)

2.5.23 LAN (RJ-45) Port1 (CN23) Pin Name Signal Type Signal Level MDI0+ DIFF MDI0- DIFF MDI1+ DIFF MDI2+ DIFF MDI2- DIFF MDI1- DIFF MDI3+ DIFF MDI3- DIFF Chapter 2 – Hardware Information... -

Page 68: Lan (Rj-45) Port2 (Cn24)

2.5.24 LAN (RJ-45) Port2 (CN24) Pin Name Signal Type Signal level MDI0+ DIFF MDI0- DIFF MDI1+ DIFF MDI2+ DIFF MDI2- DIFF MDI1- DIFF MDI3+ DIFF MDI3- DIFF Chapter 2 – Hardware Information... -

Page 69: Com Port 1 (Wafer, Optional) (Cn25)

2.5.25 COM Port 1 (Wafer, Optional) (CN25) Pin Name Signal Type Signal Level DCD1 DSR1 RTS1 ±9V ±9V CTS1 DTR1 ±9V Chapter 2 – Hardware Information... -

Page 70: Usb Ports 0 And 1 (Cn26)

2.5.26 USB Ports 0 and 1 (CN26) Pin Name Signal Type Signal level +5VSB DIFF USB0_D- DIFF USB0_D+ USB0_SSRX− DIFF USB0_SSRX+ DIFF USB0_SSTX− DIFF USB0_SSTX+ DIFF +5VSB DIFF USB1_D- DIFF USB1_D+ USB1_SSRX− DIFF USB1_SSRX+ DIFF Chapter 2 – Hardware Information... -

Page 71: Com Port 1 (D-Sub 9) (Cn27)

USB1_SSTX− DIFF USB1_SSTX+ DIFF 2.5.27 COM Port 1 (D-SUB 9) (CN27) Pin Name Signal Type Signal level ±9V ±9V ±9V Chapter 2 – Hardware Information... -

Page 72: Battery Conn (Cn28)

2.5.28 Battery CONN (CN28) Pin Name Signal Type Signal level 3.3V +3.3V 2.5.29 HDMI (CN29) Pin Name Signal Type Signal level HDMI_TX2+ DIFF HDMI_TX2- DIFF HDMI_TX1+ DIFF HDMI_TX1- DIFF HDMI_TX0+ DIFF Chapter 2 – Hardware Information... -

Page 73: Vga Port (Cn30)

HDMI_TX0- DIFF HDMI_CLK+ DIFF HDMI_CLK- DIFF DDC_CLK DDC_DATA HDMI_HPD 2.5.30 VGA Port (CN30) Pin Name Signal Type Signal level GREEN BLUE RED_GND_RTN GREEN_GND_RTN BLUE_GND_RTN Chapter 2 – Hardware Information... -

Page 74: Ddr3L So-Dimm Slot (Dimm1)

DDC_DATA HSYNC VSYNC DDC_CLK 2.5.31 DDR3L SO-DIMM Slot (DIMM1) Standard specification Chapter 2 – Hardware Information... -

Page 75: Chapter 3 - Ami Bios Setup

Chapter 3 Chapter 3 - AMI BIOS Setup... -

Page 76: System Test And Initialization

System Test and Initialization The board uses certain routines to perform testing and initialization. If an error, fatal or non-fatal, is encountered, a few short beeps or an error message will be outputted. The board can usually continue the boot up sequence with non-fatal errors. The system configuration verification routines check the current system configuration against the values stored in the CMOS memory. -

Page 77: Ami Bios Setup

AMI BIOS Setup The AMI BIOS ROM has a pre-installed Setup program that allows users to modify basic system configurations, which is stored in the battery-backed CMOS RAM and BIOS NVRAM so that the information is retained when the power is turned off. To enter BIOS Setup, press <Del>... -

Page 78: Setup Submenu: Main

Setup submenu: Main Press ‘Delete’ to enter Setup Chapter 3 – AMI BIOS Setup... -

Page 79: Setup Submenu: Advanced

Setup submenu: Advanced Chapter 3 – AMI BIOS Setup... -

Page 80: Advanced: Trusted Computing

3.4.1 Advanced: Trusted Computing Options summary: Security Device Disable Support Enable Optimal Default, Failsafe Default Enables or Disables BIOS support for security device. O.S. will not show Security Device. TCG EFI protocol and INT1A interface will not be available. SHA-1 PCR Bank Disable Enable Optimal Default, Failsafe Default... - Page 81 Pending Operation None Optimal Default, Failsafe Default TPM Clear Schedule an Operation for the Security Device. NOTE: Your Computer will reboot during restart in order to change State of Security Device. Platform Hierarchy Disabled Enabled Optimal Default, Failsafe Default Enable or disable Platform Hierarchy Storage Hierarchy Disabled Enabled...

-

Page 82: Advanced: Cpu Configuration

3.4.2 Advanced: CPU Configuration Options summary: C-States Disabled Enabled Optimal Default, Failsafe Default Enable/Disable C States. EIST Disabled Enabled Optimal Default, Failsafe Default Enable/Disable Intel SpeedStep. Turbo Mode Disabled Enabled Optimal Default, Failsafe Default Turbo Mode Power Limit 1 Enable Disabled Optimal Default, Failsafe Default Enabled Chapter 3 –... - Page 83 Enable/Disable Power Limit 1 Intel Virtualization Disabled Technology Enabled Optimal Default, Failsafe Default When enabled, a VMM can utilize the additional hardware capabilities provided by Vanderpool Technology. VT-d Disabled Optimal Default, Failsafe Default Enabled Enable/Disable CP VT-d Thermal Monitor Disabled Enabled Optimal Default, Failsafe Default Enable/Disable Thermal Monitor...

-

Page 84: Advanced: Sata Configuration

3.4.3 Advanced: SATA Configuration Options summary: Chipset SATA Disabled Enabled Optimal Default, Failsafe Default Enables or Disables the Chipset SATA Controller. The Chipset SATA controller supports the 2 black internal SATA ports (up to 3Gb/s supported per port). Port 0 Disabled Enabled Optimal Default, Failsafe Default... - Page 85 Port 1 Disabled Enabled Optimal Default, Failsafe Default Enable or Disable SATA Port SATA Port 1 Hot Plug Disabled Optimal Default, Failsafe Default Capability Enabled If enabled, SATA port will be reported as Hot Plug capable. Chapter 3 – AMI BIOS Setup...

-

Page 86: Advanced: Scc Configuration

3.4.4 Advanced: SCC Configuration Options summary: SCC eMMC Support Disabled Enabled Optimal Default, Failsafe Default Enable/Disable SCC eMMC Support eMMC Max Speed HS400 Optimal Default, Failsafe Default HS200 DDR50 Select the eMMC max Speed allowed. Chapter 3 – AMI BIOS Setup... -

Page 87: Advanced: Pci Express Configuration

3.4.5 Advanced: PCI Express Configuration Options summary: PCIE Slot(CN7) Disabled Enabled Optimal Default, Failsafe Default Control PCIE Slot (CN7) Hot Plug Disabled Optimal Default, Failsafe Default Enabled PCI Express Hot Plug Enable/Disable PCIe Speed Auto Optimal Default, Failsafe Default Gen1 Gen2 Configure PCIe Speed Chapter 3 –... -

Page 88: Advanced: Hardware Monitor

3.4.6 Advanced: Hardware Monitor Options summary: Smart Fan Disable Enable Optimal Default, Failsafe Default Enables or Disables Smart Fan. Chapter 3 – AMI BIOS Setup... -

Page 89: Hardware Monitor: Cpu Smart Fan Mode Configuration

3.4.6.1Hardware Monitor: CPU Smart Fan Mode Configuration Options summary: Fan 1 Smart Fan Manual Duty Mode Control Auto Duty-Cycle Mode Optimal Default, Failsafe Default Smart Fan Mode Select Temperature Source CPU(external) Optimal Default, Failsafe Default System Select the monitored temperature source for this fan. Duty Cycle 1 Temperature 1 Auto fan speed control. -

Page 90: Advanced: Sio Configuration

3.4.7 Advanced: SIO Configuration Chapter 3 – AMI BIOS Setup... -

Page 91: Sio Configuration: Serial Port 1 Configuration

3.4.7.1 SIO Configuration: Serial Port 1 Configuration Options summary: Use This Device Disable Enable Optimal Default, Failsafe Default Enable or Disable this Logical Device. Possible: Use Automatic Settings Optimal Default, Failsafe Default IO=3F8h; IRQ=4 IO=2F8h; IRQ=3 Allows user to change Device's Resource settings. New settings will be reflected on This Setup Page after System restarts. -

Page 92: Sio Configuration: Serial Port 2 Configuration

3.4.7.2 SIO Configuration: Serial Port 2 Configuration Options summary: Use This Device Disable Enable Optimal Default, Failsafe Default Enable or Disable this Logical Device. Possible: Use Automatic Settings Optimal Default, Failsafe Default IO=2F8h; IRQ=3 IO=3F8h; IRQ=4 Allows user to change Device's Resource settings. New settings will be reflected on This Setup Page after System restarts. -

Page 93: Sio Configuration: Serial Port 3 Configuration

3.4.7.3 SIO Configuration: Serial Port 3 Configuration Options summary: Use This Device Disable Enable Optimal Default, Failsafe Default Enable or Disable this Logical Device. Possible: Use Automatic Settings Optimal Default, Failsafe Default IO=3E8h; IRQ=11 IO=2E8h; IRQ=11 Allows user to change Device's Resource settings. New settings will be reflected on This Setup Page after System restarts. -

Page 94: Sio Configuration: Serial Port 4 Configuration

3.4.7.4 SIO Configuration: Serial Port 4 Configuration Options summary: Use This Device Disable Enable Optimal Default, Failsafe Default Enable or Disable this Logical Device. Possible: Use Automatic Settings Optimal Default, Failsafe Default IO=2E8h; IRQ=10 IO=3E8h; IRQ=10 Allows user to change Device's Resource settings. New settings will be reflected on This Setup Page after System restarts. -

Page 95: Sio Configuration: Parallel Port Configuration

3.4.7.5 SIO Configuration: Parallel Port Configuration Options summary: Use This Device Disable Optimal Default, Failsafe Default Enable Enable or Disable this Logical Device. Chapter 3 – AMI BIOS Setup... -

Page 96: Advanced: Power Management

3.4.8 Advanced: Power Management Options summary: Power Mode ATX Type Optimal Default, Failsafe Default AT Type Select system power mode Power Saving(ERP) Disabled Optimal Default, Failsafe Default Control Enabled Configure power mode for power saving function. Restore AC Power Last State Optimal Default, Failsafe Default Loss Always On... - Page 97 from S5 Fixed Time Select system power mode Chapter 3 – AMI BIOS Setup...

-

Page 98: Advanced: Digital Io Port Configuration

3.4.9 Advanced: Digital IO Port Configuration Options summary: DIO Port* Output Input Set DIO as Input or Output Output Level High Optimal Default, Failsafe Default Set output level when DIO pin is output Chapter 3 – AMI BIOS Setup... -

Page 99: Setup Submenu: Chipset

Setup submenu: Chipset Chapter 3 – AMI BIOS Setup... -

Page 100: Chipset: North Bridge

3.5.1 Chipset: North Bridge Chapter 3 – AMI BIOS Setup... -

Page 101: North Bridge: Lvds Panel Configuration

3.5.1.1 North Bridge: LVDS Panel Configuration(LVDS2 only available for 2 LVDS Sku) Options summary: LVDS Disabled Enabled Optimal Default, Failsafe Default Enable/Disabled this panel. LVDS Panel Type 640x480@60Hz 800x480@60Hz 800x600@60Hz 1024x600@60Hz 1024x768@60Hz Optimal Default, Failsafe Default 1280x768@60Hz 1280x800@60Hz Chapter 3 – AMI BIOS Setup... - Page 102 1280x1024@60Hz 1366x768@60Hz 1440x900@60Hz 1600x1200@60Hz 1920x1080@60Hz 1920x1200@60Hz Select LCD panel used by Internal Graphics Device by selecting the appropriate setup item. Color Depth 18-bit Optimal Default, Failsafe Default 24-bit 36-bit 48-bit Select panel type Backlight Type Normal Optimal Default, Failsafe Default Inverted Select backlight control signal type Backlight Level...

- Page 103 Select backlight control level Backlight PWM Freq 100Hz 200Hz 220Hz Optimal Default, Failsafe Default 500Hz 1KHz 2.2KHz 6.5KHz Select PWM frequency of backlight control signal Chapter 3 – AMI BIOS Setup...

-

Page 104: Setup Submenu: Security

Setup submenu: Security Change User/Supervisor Password You can install a Supervisor password, and if you install a supervisor password, you can then install a user password. A user password does not provide access to many of the features in the Setup utility. If you highlight these items and press Enter, a dialog box appears which lets you enter a password. -

Page 105: Setup Submenu: Boot

Setup submenu: Boot Options summary: Quiet Boot Disabled Enabled Optimal Default, Failsafe Default EnableDisable showing boot logo. Monitor Mwait Disable Enabled Auto Optimal Default, Failsafe Default Enable/Disable Monitor Mwait. To install Linux OS, please set this item to disable. Ipv4 PXE Support Disabled Optimal Default, Failsafe Default Enabled... -

Page 106: Setup Submenu: Exit

Setup submenu: Exit Chapter 3 – AMI BIOS Setup... -

Page 107: Chapter 4 - Drivers Installation

Chapter 4 Chapter 4 – Drivers Installation... -

Page 108: Driver Download/Installation

Driver Download/Installation Drivers for the GENE-APL6 can be downloaded from the product page on the AAEON website by following this link: https://www.aaeon.com/en/p/embedded-single-board-computers-gene-apl6 Download the driver(s) you need and follow the steps below to install them. Step 1 – Install Chipset Drivers Open the Step1 - Chipset folder followed by SetupChipset.exe Follow the instructions Drivers will be installed automatically... - Page 109 Step 5 – Install TXE Driver Open the Step5 - TXE folder followed by SetupTXE.exe Follow the instructions Drivers will be installed automatically Step 6 – Install Touch Driver Open the Step6 - Touch folder followed by Setup.exe Follow the instructions Drivers will be installed automatically Step 7 –...

-

Page 110: Appendix A - Watchdog Timer Programming

Appendix A Appendix A - Watchdog Timer Programming... -

Page 111: Watchdog Timer Registers

Watchdog Timer Registers Table 1 : Watch dog relative IO address Default Value Note I/O Base I/O Base address for Watchdog operation. 0xA10 Address This address is assigned by SIO LDN7, register 0x60-0x61. Table 2 : Watchdog relative register table Register Offset BitNum... -

Page 112: Watchdog Sample Program

A.2 Watchdog Sample Program ****************************************************************************** // WDT I/O operation relative definition (Please reference to Table 1) #define WDTAddr 0x510 // WDT I/O base address Void WDTWriteByte(byte Register, byte Value); byte WDTReadByte(byte Register); Void WDTSetReg(byte Register, byte Bit, byte Val); // Watch Dog relative definition (Please reference to Table 2) #define DevReg 0x00 // Device configuration register #define WDTRstBit 0x80 // Watchdog WDTRST# (Bit7) - Page 113 VOID AaeonWDTEnable (){ WDTEnableDisable(1); // Procedure : AaeonWDTConfig VOID AaeonWDTConfig (byte Counter, BOOLEAN Unit){ // Disable WDT counting WDTEnableDisable(0); // Clear Watchdog Timeout Status WDTClearTimeoutStatus(); // WDT relative parameter setting WDTParameterSetting(Timer, Unit); VOID WDTEnableDisable(byte Value){ If (Value == 1) WDTSetBit(TimerReg, EnableBit, 1); else WDTSetBit(TimerReg, EnableBit, 0);...

- Page 114 VOID WDTWriteByte(byte Register, byte Value){ IOWriteByte(WDTAddr+Register, Value); byte WDTReadByte(byte Register){ return IOReadByte(WDTAddr+Register); VOID WDTSetBit(byte Register, byte Bit, byte Val){ byte TmpValue; TmpValue = WDTReadByte(Register); TmpValue &= ~(1 << Bit); TmpValue |= Val << Bit; WDTWriteByte(Register, TmpValue); ******************************************************************************* Appendix A – Watchdog Timer Programming...

-

Page 115: Appendix B - I/O Information

Appendix B Appendix B - I/O Information... -

Page 116: I/O Address Map

I/O Address Map Appendix B – I/O Information... - Page 117 Appendix B – I/O Information...

-

Page 118: Memory Address Map

Memory Address Map Appendix B – I/O Information... -

Page 119: Irq Mapping Chart

IRQ Mapping Chart Appendix B – I/O Information... - Page 120 Appendix B – I/O Information...

- Page 121 Appendix B – I/O Information...

- Page 122 Appendix B – I/O Information...

-

Page 123: Appendix C - Mating Connectors

Appendix C Appendix C – Mating Connectors... -

Page 124: List Of Mating Connectors And Cables

List of Mating Connectors and Cables Mating Connector Connector Available Function Cable P/N Label Cable Vendor Model no External +5VSB Power Input PHR-3 ATX Cable 170220020B PS_ON# +5Vout 2 Pins For PHR-2 1702150155 Connector HDD Power +9~24V Vin Power 1702002010 Connector Cable SATA... - Page 125 LVDS DF13-30DS- CN13 HIROSE Connector 1.25C Digital I/O CN16 Neltron 2026B-10 Connector LVDS CN17 Inverter PHR-5 Connector LVDS DF13-30DS- CN18 HIROSE Connector 1.25C USB Port USB Wafer CN19 Molex 51021-0500 1700050207 Connector Cable USB Port USB Wafer CN20 Molex 51021-0500 1700050207 Connector Cable...

-

Page 126: Appendix D - Digital I/O Ports

Appendix D Appendix D – Digital I/O Ports... -

Page 127: Digital I/O Register

Digital I/O Register Appendix D – Digital I/O Ports... - Page 128 Appendix D – Digital I/O Ports...

-

Page 129: Digital I/O Sample Code (4 In 4 Out, 2 Low 2 High)

Digital I/O Sample Code (4 in 4 out, 2 low 2 high) Outportb(0x2E,0x87); //enter configuration Outportb(0x2E,0x87); Outportb(0x2E,0x07); //set LDN Outportb(0x2F,0x06); Outportb(0x2E,0xA0); //GPIO set 5 register Outportb(0x2F,0xF0); Outportb(0x2E,0xA1); //GPIO output data register Outportb(0x2F,0x30); Outportb(0x2E,0xAA); //exit configuration Appendix D – Digital I/O Ports...